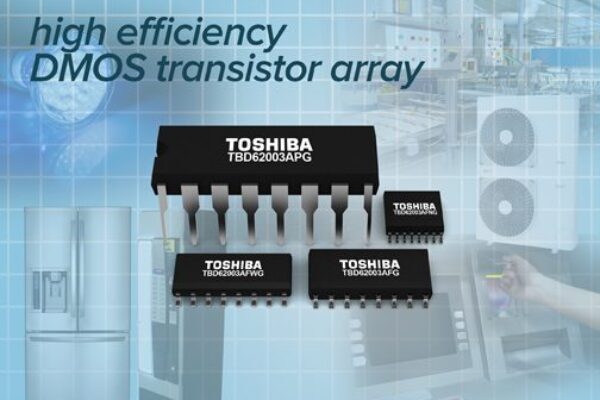

The adoption of DMOS FET type output driver for the new products ensures the devices meet requirements for high efficiency and reduced power loss as DMOS FETs do not require a base current. ON-resistance is kept low and the output block can accept high voltages and currents, with an absolute maximum rating of 50V / 0.5A.

This approach enables the TBD62xxxA series to cut power loss by about 40% compared with the preceding TD62xxxA series of bipolar transistor arrays (Ta = 25C and IOUT = 200mA). Toshiba has used BiCD technology in the creation of the new series as it allows the integration of bipolar, CMOS and DMOS devices. The new generation series consists of 24 products that are compliant with various VIN(ON) standard voltages.

The TBD62003A series features min. 14V VIN(ON) to support 14V to 25V PMOS input signals. The TBD62503A series features min. 2.5V VIN(ON) supporting transistor-transistor logic (TTL) and 3V/5V CMOS input signals. The TBD62004A series features min. 7.0V VIN(ON) for 6V to 15V PMOS and 5V CMOS input signals.

The devices will be available in packages to suit a variety of needs including DIP. SOP/SOL for surface mounting and small SSOP (0.65 mm pitch) for space saving. Mass production across the complete line-up is scheduled to start during the second half of 2015.

Toshiba Electronics Europe; www.toshiba.semicon-storage.com

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News