Automating analog design requires that constraints such as symmetry and matching, noise coupling, and the use of shielding be part of the automated flow. Commercial routers capable at the device level can handle some of these types of constraints, but handling power net routing is typically done by planning manually.

In the digital world, power distribution methodology is much easier. With row-based, standard cell placement and routing (P&R), and the availability of relatively many metal layers, power rings and meshes can be easily generated automatically. True, this can become more complicated as designers seek to use less power by using power switches and have multiple voltage domains, but there are well established EDA tools to help designers analyze and optimize power distribution schemes.

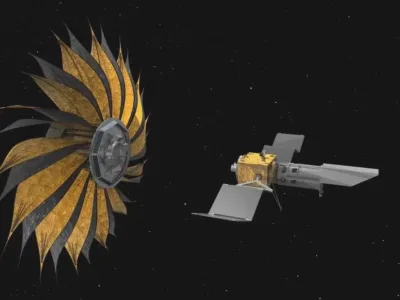

For small analog IP blocks, power routing can often be relatively simple. A common approach is to start with a “template” cell defining the desired block size, pin positions, and VDD/VSS rails, typically at the top and bottom of the block. However, even for relatively simple blocks, the power hookup to devices has generally been done manually. Actually, there is no reason why a mesh-type structure can’t be used; for example, two layers are shown in Figure 1, which shows VDD/VSS rails at the top and bottom of the block with an irregular H-shaped mesh in the center. The key to achieving this is the ability to place and route devices, signal nets, and power nets simultaneously. Device S/D pins can directly strap to the power mesh to give a clean routing style.

Widths of power tracks need to be considered carefully for analog layout. As geometries get smaller, tapering of power nets may be required since uniform-width nets may be too wide for individual transistor tap-offs, but too narrow due to electromigration rules for higher current portions of the nets. In this case, careful consideration of current flow is required in order to size the net segments appropriately. (For more details visit “Current-driven wire planning for electromigration avoidance in analog circuits.”) Simulation results of transistor pin currents are required here in order to accurately model the current requirements of the power nets (and potentially the signal nets, too).

Automated power routing mesh for an analog block

Another common approach is to use combined power and guard rings/rails. The “variable mesh” approach can also be used here, although it becomes more complex as guard rings require single layer (i.e., wrong way) preferred directions. Again, device S/D pins can tap into guard rings to simplify local power routing.

A further development would be to support hierarchical power routing, where power pins on the lower-level blocks strap into the higher-level cells’ mesh. Once again, actual net widths need to be computed accurately for this approach.

As can be seen, automated analog routing presents challenges compared to digital power distribution. However, with new techniques and methodologies, automation is possible, and the goal of speedier design iterations can be achieved, enhancing productivity.

Keith Sabine, product manager for analog solutions at Pulsic Ltd. (Bristol, England), has 35 years of experience in the semiconductor and EDA industries, starting out as a bipolar designer at Fairchild Semiconductor before moving into CMOS process development and characterization at Plessey Semiconductors. His EDA career has included time at Cadence, Simplex, Apache, and now Pulsic.

This article first appeared on EE Times’ Planet Analog website.

Related links and articles:

News articles:

Analog synthesis remains remote

Circuit matching and analog layout

Time for custom, analog design tools to automate?

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News