Searchable 4K mobile imaging soon a commodity

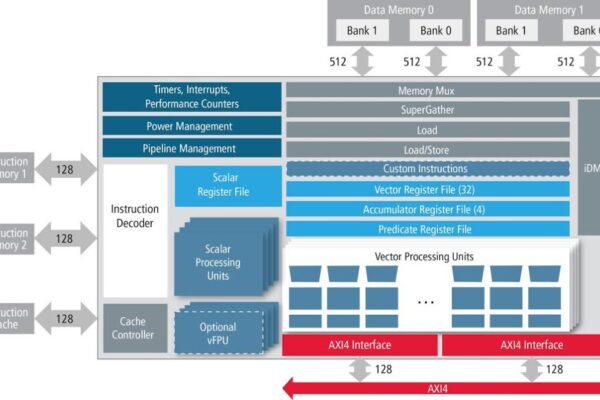

The new DSP core was built from the ground up for applications requiring ultra-high memory and operation parallelism to support complex vision processing at high resolution and high frame rates.

As such, it is well suited for off-loading vision and imaging functions from the main CPU to increase throughput and reduce power. End-user applications that can benefit from the DSP’s capabilities include image and video enhancement, stereo and 3D imaging, depth map processing, robotic vision, face detection and authentication, augmented reality, object tracking, object avoidance and advanced noise reduction.

The Tensilica Vision P5 DSP core includes a significantly expanded and optimized Instruction Set Architecture (ISA) targeting mobile, automotive advanced driver assistance systems (or ADAS, which includes pedestrian detection, traffic sign recognition, lane tracking, adaptive cruise control, and accident avoidance) and Internet of Things (IoT) vision systems.

The advances in the Tensilica Vision P5 DSP further improve the ease of software development and porting, with comprehensive support for integer, fixed-point and floating-point data types and an advanced toolchain with a proven, auto-vectorizing C compiler. The software environment also features complete support of standard OpenCV and OpenVX libraries for fast, high-level migration of existing imaging/vision applications with over 800 library functions.

Among the key new features enabling this drastic performance increase is the wide 1024-bit memory interface with SuperGather technology for maximum performance on the complex data patterns of vision processing.

With The SuperGather technology operates in parallel and supports the reads and writes of many non-contiguous address cells, improving non-uniform access algorithms such as image warping, edge tracing, non-rectilinear patch access.

The DSP supports up to 4 vector ALU operations per cycle, each with up to 64-way data parallelism, up to 5 instructions issued per cycle from 128-bit wide instruction delivering increased operation parallelism, and enhanced 8-,16- and 32-bit ISA tuned for vision/imaging applications.

An optional 16-way IEEE single-precision vector floating-point processing unit delivers 32GFLOPs at 1GHz.

As a real-life example, Dennis Crespo, Director of Product Marketing for the Cadence Tensilica Imaging Group mentioned a customer doing research in deep neural networking on the server side, to perform big data analysis on image data. The unnamed customer was able to move from a power-hungry 250W GPU array solution to a 4W DSP implementation using eight Vision P5 DSP cores.

"In smartphones, the new DSP core could displace some of the GPU silicon, trading off your typical 5W mobile GPU solution for a 300mW DSP", Crespo said, commenting on the need for more digital signal processing as pixel sizes shrink and signal to noise ratio gets worse.

"4K video which used to be seen only in the professional domain is now moving to smartphones" he added, saying that professional use cases are pushing image resolutions to 50 or even 100 Mpixels.

According to Crespo, the new IP is the sort of DSP solution needed for image data mining or even audio data mining that, when coupled with machine learning, could figure out what users may want to buy at what time. This is the sort of predictive consumer analysis that advertisers are expecting from big data.

Another promising mass market could be drones, as according to Crespo, most of the object detection algorithms found in automotive could directly translate into the drone market. Such a DSP could be integrated into a new SoC for drone control systems, to alleviate poor operator performance and smooth out the flight and video recording experience.

More information on the Tensilica Vision P5 DSP at https://www.cadence.com/news/TensilicaVisionP5.

Related articles:

Virtual reality a real driver for GPUs, says ARM

Cadence and ARM strategic partners on IP

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News