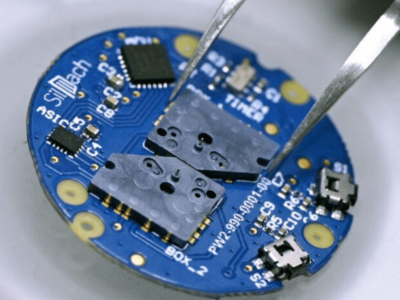

The design integrates three stacked dies, integrating a Wide I/O DRAM memory with a 512bit interface stacked on top of two identical SOC logic die that incorporate multiple processor cores on each die. Through-silicon vias (TSVs) connect these three die together and in order to minimize the impact of the TSVs on signal integrity, the 3D stack uses an asynchronous NoC for both die-to-die and intra-die communications.

The 3D-friendly NoC employs asynchronous serial links and achieves 550M transfers/sec throughput in the 2D (intra-die) direction, and 200M transfers/sec in the 3D (inter-die) direction. Together with the high throughput and low power Wide I/O memory interface, this advanced three-die 3D prototype represents a first proof of concept, clearly demonstrating how these technologies can be employed to efficiently stack memory and logic for future 3D multi-processor architectures, say Pascal Vivet, researcher for CEA-Leti and Vincent Guerin, senior digital design engineer, ST-Ericsson who are presenting the paper at the 3D Architectures for Semiconductor Integration and Packaging Conference in San Francisco.

ST-Ericsson developed WIOMING application processor SOC integrated with a Wide I/O memory interface that is used in the stack. Combined with Wide I/O technology, TSV and fine-pitch bumping technologies permit massive, high-bandwidth interconnect between the DRAM and SOC with very low capacitive and inductive loading. This approach also reduces interface power dissipation in the DRAM and logic die. The ST-Ericsson WIOMING SOC provides 12.8GBytes/s of memory bandwidth – a 50 percent increase over the latest available dual channel LPDDR2 solutions at 533MHz at 20% less power. Increasing the DRAM interface clock frequency to 266MHz and switching to DDR (dual data rate) mode will allow ST-Ericsson to create designs that deliver more than 34GBytes/s in future products, enabling unprecedented graphics and CPU performance in product such as smartphones and tablets.

The project also included design tool vendor Cadence for the tools and methodologies necessary for enabling this breakthrough three-layer 3D IC. The company developed an automated and integrated 3D/TSV design solution using Encounter Digital Implementation (EDI) System, Virtuoso Analog Design Environment and QRC parasitic extraction tool. The project design team then used these tools to address complex timing, signal integrity, and thermal challenges in the 3D design.

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News