The automotive market stands out amidst other application segments in that it has particular high requirements with regards to high integration as well as specific safety and reliability. From the engineering perspective, the integration and performance requirements translate into designs that increasingly make use of Systems-on-chip (SoCs) with multiple heterogeneous microprocessors along with applications logic, memory and interfaces in a single package. Synopsys supports this design trend in that it extends its DesignWare IP portfolio with a range of IP blocks that cast the most promising and future-oriented functions into silicon by means of RTL code or hard IP.

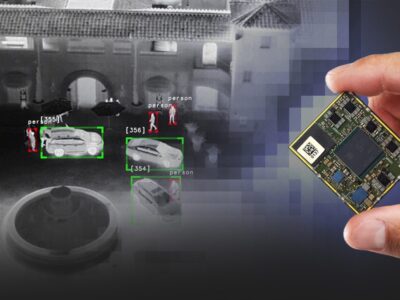

The offering includes Ethernet Audio Video Bridging (AVB), Low-power DDR4 memory, non-volatile memories, data converters and other functional units, all powered by Synopsys’ ARC microprocessor architecture. In addition, the offering includes a range of interface IP mostly used in the infotainment domain and Advanced Driver Assistance System (ADAS) applications like HDMI, PCI Express and USB. Most of these building blocks are pre-certified according to the safety standard ISO 26262, ASIL level B. While the B level is only the third-highest of four levels and thus does not inherently include the most safety-critical applications like power steering or everything around semi- or full automated driving, this does not rule out that the IP can be used in such systems, explained Jai Durgam, Synopsys Group Director of Field Applications Engineering, in an interview with eeNews Europe. In such cases however the design needs to be certified individually.

In any case, already the IP in question is delivered with safety packages that include failure mode effects and diagnostic analysis reports as well as safety plans and manuals, giving designers the documentation required to complete their own certification process. In addition, the development process for the Synopsys IP also supports the TS 16949 standard documentation requirements. The entire safety certification process has been developed in close collaboration with certification services provider SGS-TÜV Saar. “Functional safety, represented by ASIL B Ready certification, is crucial for new automotive applications such as ADAS”, says Wolfgang Ruf, product manager at SGS-TÜV Saar. “Meeting ISA standards is key to demonstrating that an SoC, including its components, delivers enhanced processes for functional safety. By investing in the development of IP that meets strict certification guidelines, Synopsys is enabling SoC designers to faster meet their automotive design and certification objectives”.

Related articles:

Synopsys looks to hardware for faster ARC core designs

IP builds automotive-grade-0, non-volatile memory in 75% less area

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News