Xilinx unveils low-cost RTL synthesis tool optimized for its 28nm FPGA fabric

The Vivado Design Suite, which took the company over 4 years of development (across more than 500 sofware engineers) to ensure a tight optimization of the synthesized RTL output for the fabric of Xilinx’ largest 28nm FPGAs, is said not only to speed the design of programmable logic and I/O, but also to accelerate programmable systems integration and implementation into devices incorporating 3D stacked silicon interconnect technology, ARM processing systems, Analog Mixed Signal (AMS), and a significant percentage of semiconductor IP cores.

Senior director of design methodology marketing at Xilinx, Tom Feist who was in Paris to present the new tool (and also to run a Marathon) explained eeNews Europe that although this had required a significant investment, the company was now able to offer a complete synthesis tool suite at a fraction of the cost typically associated with the ASIC design tools necessary for multi-million gate designs. Feist commented that existing tools from third-party EDA vendors were becoming prohibitively expensive for the small and medium businesses willing to take advantage of the high performance and the low non-recurring engineering costs of today’s FPGAs.

Of course, the terms of license would not allow users to design outside Xilinx’ FPGA environment, as it is not Xilinx’ aim to compete head-to-head with the big EDA vendors. But many “ASIC refugees” will appreciate, as Feist jokingly stated, evoking engineers who for cost reasons move their original ASIC intent to an FPGA. Available for only a couple of thousand dollars, the Vivado Design Suite has been beta tested with more than 100 customers and Alliance Program members over the past 12 months, including customers using Xilinx’ stacked silicon interconnect-based Virtex-7 devices. As Feist explained, while a lot of tools blast back the design to the finest grain and then try to stitch things up onto hardware, by designing a modern multidimensional analytic placement engine using state-of-the-art EDA algorithms, Xilinx was able to tune its tools directly for its FPGA architecture.

The highly integrated design environment comes with a completely new generation of system-to-IC level tools, all built on the backbone of a shared scalable data model and a common debug environment. It is also an open environment based on industry standards such as the AMBA4 AXI4 interconnect specification, IP-XACT IP packaging metadata enabling users to share and easily interconnect new IP, the Tool Command Language (Tcl), Synopsys Design Constraints (SDC) and others that facilitate design flows tailored to the user’s needs. Xilinx claims its Vivado tools are architected to enable the combination of all types of programmable technologies and scale up to 100-million-ASIC equivalent gate designs, enough for the next decade of designs according to Feist.

To address integration bottlenecks, the Vivado IDE includes electronic system level (ESL) design tools for rapidly synthesizing and verifying C based algorithmic IP; standards based packaging of both algorithmic and RTL IP for reuse; standards based IP stitching and systems integration of all types of system building blocks. The environment supports the verification of blocks and systems with a 3-fold simulation speed, while hardware co-simulation provides 100X more performance.

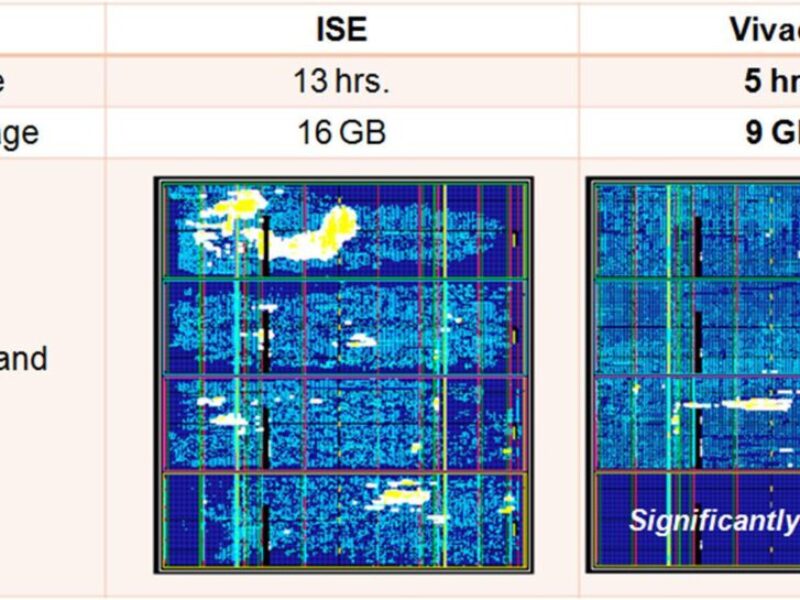

To circumvent implementation bottlenecks, Vivado includes a hierarchical device editor and floor planner, a 3 to 15X faster logic synthesis tool (depending on the level of optimization) with support for SystemVerilog, and a 4X faster, more deterministic place and route engine that uses analytics to minimize a ‘cost’ function of multiple variables such as timing, wire length and routing congestion.

Fig. 1: The multidimensional analytic algorithm optimizes layouts for best timing, congestion and wire length. Comparing the same design as routed on the Zynq emulation platform by Xilinx’ ISE and Vivado tools.

Incremental flows allow for engineering change order (ECO) induced changes to be quickly processed by only re-implementing a small part of the design, while preserving performance. Finally, leveraging the new shared scalable data model, the tools provide power, timing and area estimates at every stage of the design flow, enabling up front analysis and then optimization with integrated capabilities such as automated clock gating.

The Vivado Design Suite version 2012.1 is available as part of an early access program. Public access will commence with version 2012.2 early this summer, followed by WebPACK availability and Zynq-7000 Extensible Processing Platform support later in the year. ISE Design Suite Edition customers with current support will be provided the new Vivado Design Suite Editions in addition to ISE at no additional cost.

Visit Xilinx at www.xilinx.com/design-tools

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News

If you enjoyed this article, you will like the following ones: don't miss them by subscribing to :

eeNews on Google News